Merhabalar,

Bugün verilogda D-FF, sayısal tasarımdaki adıyla register tasarlayacağız. Öncelikle kodumuzu inceleyelim.

module d_ff(a,b,clk);

input a;

input clk;output reg b;

always@(posedge clk) begin

b<=a;

endendmodule

Bu kodda diğer kodlardan farklı olarak always yapısı bulunmaktadır. Bu yapı parantez içinde bulunan durum gerçekleştiği anda veya parantez içinde bulunan sinyallerde değişiklik olduğu durumlarda içindeki işlemin yapılmasını sağlar.

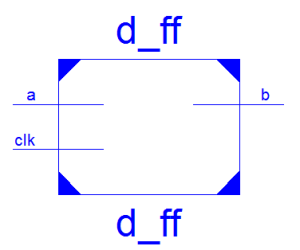

Bu örneğimizde görülüğü gibi clk işaretinin yükselen kenarında (posedge- positive edge) aşağıdaki işlemlerin yapılmasını sağlar. İşlemimiz a girişinin b çıkışına atanmasıdır. Aslında a D-FF’in girişi, b çıkışı olmaktadır. Always yapılarında dikkat edilmesi gereken, tüm atama yapılan işaretler (örneğin b sinyali) yukarıda tanımlanırken reg ifadesi ile tanımlanmalıdır. Tasarımımızın RTL şematiği aşağıdadır.

Böylece ilk ardışıl (sequential) devremizi yapmış bulunuyoruz. Bir sonraki çalışmada always yapısını kullanımıyla ilgili farklı yapılar sunmaya çalışacağım.

İyi çalışmalar